使用JEDEC热度量计算芯片温度(无附加散热器)

By: Bruce Guenin

介绍

JEDEC单芯片封装热度指标被广泛用作表征半导体封装热性能的手段。它们将均匀加热的半导体芯片的峰值温度(结温\(T_j\))与沿着热流路径的特定区域的温度相关联。这些指标的值由标准化条件下的温度测量确定,详细规定了测试方法,测试板和热环境[1]。

这些指标采用欧姆定律电阻计算的形式。使用以下公式计算热阻: $$ \theta_{jx}=\frac{T_j-T_x}{P} $$

其中\(T_x\)是热量流入的区域的温度,\(P\)是器件的总发热功率。

a)自然对流

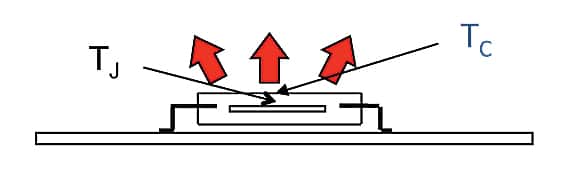

b) 强制对流,结到外壳

c)传导散热,结到电路板

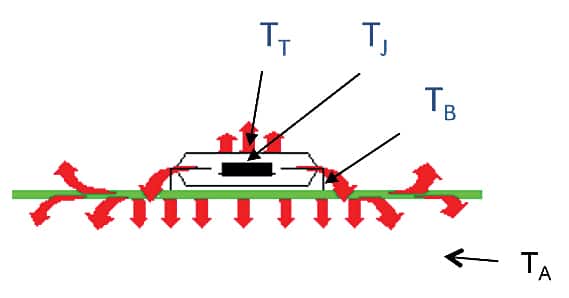

图1显示了安装在四个JEDEC标准测试环境的测试板上的封装典型热流路径的图表。指示的温度测量位置是由相应测试标准为每个环境指定的。

结到壳和结到板的测试环境迫使几乎100%的热量沿指定的路径流动。

自然对流和强制对流环境与其他两种电子产品的大多数最终使用环境有着非常相似的地方。在这些对流冷却的环境中,封装将一部分散发的热量从空气的顶部表面中排出,其余部分则散发到板上。对于大多数应用来说,这两条路径几乎涵盖了包裹外的所有热流。

还有另一类JEDEC热性能指标,对于计算应用环境的结温非常有用。它们被称为热特性参数,由希腊字母\(\Psi\)(发音为“psi”)表示[1]。它们的计算方式与\(\theta\)指标相同,如下所示:

热特性参数\(\Psi\)与热阻\(\theta\)之间的关键差异在于:在前者的情况下,只有部分热量流向由温度\(T_x\)表示的区域。当\(T_x\)和\(P\)已知时,它们可以用来估计\(T_j\) 。最相关到我们的目的的度量是\(\Psi_{jt}\)和\(\Psi_{jb}\),其中\(T_{T}\)表示在封装的顶部中心的温度和\(T_{B}\)是板的温度,上至所述封装内焊接的表面迹线测量距封装边缘1毫米。痕迹应该在其一侧的中间与包装接触。

图2a。热电阻网络代表结到板到空气路径和结到壳到空气路径。

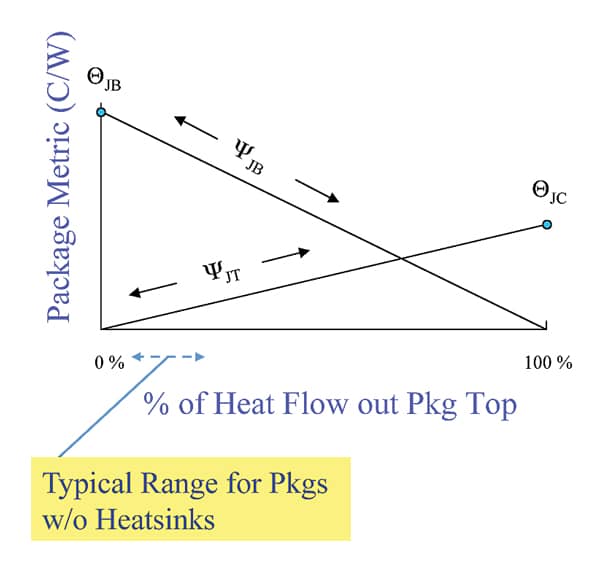

图2b。图解说明了\(\theta\)和等效\(\Psi\)值之间的关系,作为热量从封装顶部流出到空气的函数。

可以利用一个简单的模型来深入了解封装/电路板组件的散热性能。图2a表示使用简单热阻网络的两条热流路径。这两条路径之间的总热量的划分最终是由沿每条路径的总热阻,这是等于Θ确定JC +Θ CA和Θ JB +Θ BA分别。电阻Θ CA和Θ BA表示热输送的分别从封装和板,上方的效率,环境空气,并且各自的空气速度的函数。除非散热器附接至包装的顶部,Θ BA将比Θ小得多CA由于对相比于包装的顶部的热交换在空气中的板表面的更大的区域。这个电路的检查表明,在空气中的速度的变化将修改Θ的值CA和Θ BA,导致在功率沿两个路径并且在Ψ后续改变流动变化Ť和Ψ 乙和\(\Psi_{JT}\) 和\(\Psi_{JB}\)。

在图2b的图表说明Ψ之间的相互关系JT和\(\Psi_{JB}\)作为流出的包(P顶部的电源TOP)的变化。它显示了如何在P的值小TOP,几乎所有的电力流向板和\(\Psi_{JB}\)接近Θ的值JB。相反,如果一个散热片附接至包装的顶部,使得P TOP几乎等于总功率,则\(\Psi_{JT}\)近似于Θ的值JC。

本文探讨了这些不同指标之间的关系以及如何使用这些指标1)用现有的电子系统来估算结温或2)在设计过程中预测系统的结温。

JEDEC热测量在强制空气测试环境中的行为

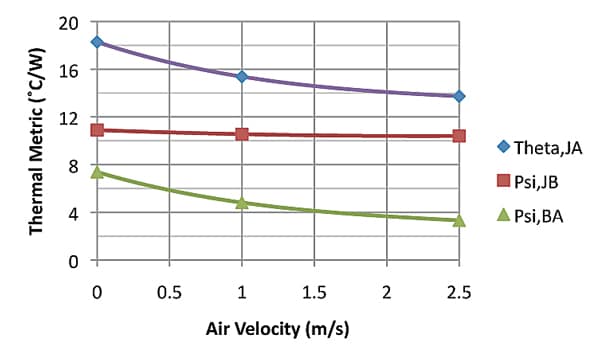

图3a包含在35 x 35 mm,388球,PBGA封装上测量的几个度量图,其中包含两个铜平面的4层叠层。该封装被安装到一个100平方毫米的JEDEC标准电路板上,并带有两个铜内部平面。两个上部曲线是\(\theta_{JA}\)和\(\Psi_{JB}\)。第三曲线,\(\Psi_{BA}\)是通过减去Ψ得到JB从\(\theta_{JA}\)。

的\(\theta_{JA}\)曲线显示在空气速度的依赖性显著,主要是由于电路板的作用,作为一个散热片,因为它进行热交换以在其整个区域中的对流气流。

相比之下,\(\Psi_{JB}\)几乎是独立的空气流速。这是因为大部分来自接点的热流通过内部传导过程流向板。这表明,\(\Psi_{JB}\)是相对坚固的,并且是在封装的具有对流环境的贡献相对较小的热传导效率的有效措施。

在\(\Psi_{BA}\)曲线表现在空气速度最大的灵敏度,因为根据定义,它的幅度是在板的耦合传导对流冷却机构的直接结果。

在\(\Psi_{BA}\)曲线表现在空气速度最大的灵敏度,因为根据定义,它的幅度是在板的耦合传导对流冷却机构的直接结果。

图3.带有4层JEDEC标准电路板的35X35mm,388球PBGA封装的热测试结果与空气流速的关系。

图3.带有4层JEDEC标准电路板的35X35mm,388球PBGA封装的热测试结果与空气流速的关系。

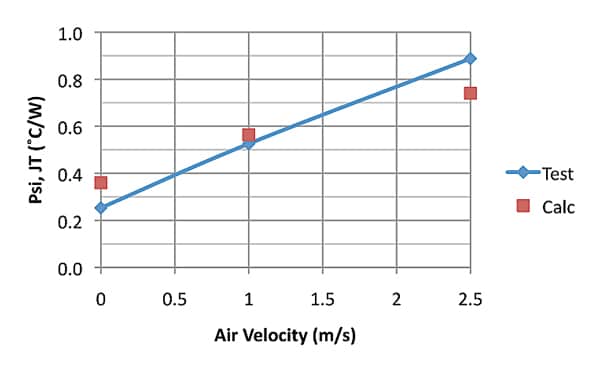

图3b曲线\(\Psi_{JT}\)与空气速度。正如所料,它是一个敏感的空气速度函数,因为从模具通过包覆成型塑料盖的热流量与一定的空气流速相关的传热系数成正比。一个还注意到在空气速度高达2.5米/秒,\(\Psi_{JT}\) 是小于1℃/ W。这意味着,对于适度的功率水平,封装顶部中心的温度只比连接点略低。这用于减少在计算T中的错误Ĵ由于ΔT的值JT使用等式2随后将是一个非常小的校正,以增加T的大得多的测量值来计算Ť。

该分析导致这样的结论:Ψ的主要价值JB是,它是适度稳健,并且可以用来预测结和一个板,当耗散功率是已知之间的温度差。相反,如果在他面前有一个操作电子系统,并且希望通过测量封装顶部的温度来了解塑料封装中的管芯温度,则\(\Psi_{JT}\)更有用。

它并不总是Ψ情况JT由包供应商提供。在这种情况下,计算起来相对容易。

在前面一列中,推导出以下等式[6]: $$ \Psi_{JT}=\frac{h\theta_{JA}t_{EMC}}{K_{EMC}} $$ 其中\(h\)是在感兴趣的空气速度下计算的传热系数的值,并且\(t_{EMC}\)和\(K_{EMC}\)是模具上方的环氧树脂模塑料的厚度及其导热率。在本例中,\(t_{EMC}\)和\(K_{EMC}\)分别为0.86 mm和0.7 W / mK。

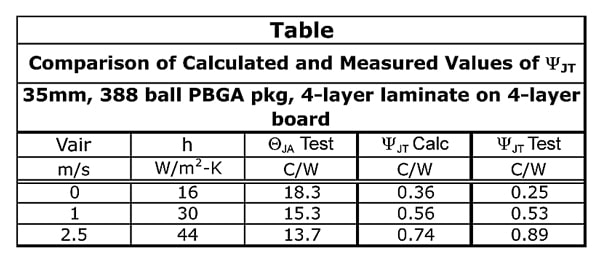

Ψ的计算值JT绘制在图3b和也列在与剩余的参数输入沿下表入等式3Ψ的测量和计算值之间的差异JT是小的绝对值。

使用\(\Psi_{JB}\)预测结温

为了成功地使用\(\Psi_{JB}\)度量在预测结温,需要知道\(T_B\)并在应用程序的耗散功率和空气的流动条件。

有很多方法可以用来估算\(T_B\)。其中的选择是建立一个负载板,具有实际电路板的总体尺寸和电导率,并使用加热器预期的热负荷,以及适当的冷却方法[7]。或者,可以创建适当的计算流体动力学(CFD)或板的有限元或有限差分传导模型,并考虑热负荷和冷却。最后,如果需要快速而适度的解决方案,则可以通过在模型中包含单封装板来估算电路板温度。适当的电路板尺寸将取决于实际电路板的面积,乘以感兴趣的器件功率与电路板上所有器件的总功率的比值[8]。

Ψ的有用JB,这是在一个标准的测试环境中产生,以结温的预测中的事实,在两种环境下,存在施加到封装的顶部,对流边界条件的应用程序的结果,从理论上讲,将以相同的风速。

一般来说,从模具到封装顶部的单个电阻连接对于任意的边界条件而言并不总是准确的。为了具有稳健的边界条件独立性,需要一个紧凑的热模型,例如[9]。

无论是在JEDEC标准多层板上还是在应用板上进行测试,对于给定的封装来说,致力于开发\(\Psi_{JB}\)标准的初始工作都表现出了相似的值[10]。

结论

的JEDEC标准热特性参数,\(\Psi_{JB}\)和\(\Psi_{JT}\),可以在促进结温在半导体封装的计算既为实时系统,并且还在预测计算是有价值的。通过测量确定的这些指标通过提供模拟结温度的方便实验验证来补充纯热模拟方法。

参考

\1. JEDEC标准JESD51-12,“电子封装散热信息报告和使用指南”。所有JEDEC标准可从www.jedec.org免费下载。 \2. JEDEC标准JESD51-2A“集成电路热测试方法环境条件 - 自然对流(静止空气)” 。3. JEDEC标准JESD51-6,“集成电路热测试方法环境条件 - 强制对流(移动空气)”。 \4. JEDEC标准JESD51-14,“通过单通道热流测量半导体器件热阻结的瞬态双接口测试方法” 。5. JEDEC标准JESD51-8“集成电路热测试方法环境条件 - 交界处“。 \6. B. Guenin,“确定塑料半导体封装中的结温,第一部分,”ElectronicsCooling,第5号,第2号,1999年5月 。7. B. Siegal,“热负载板设计考虑因素,”ElectronicsCooling,卷。18,第3期,九月,2009年 8 B. Guenin,“定性上组装印刷电路板上的封装,” ElectronicsCooling,卷。第7期,第2期,2001年5月 。9. S. Shidore,“电子设计中的紧凑型热模型”ElectronicsCooling,Vol。13,第2号,月,2007年 10 B.木“在预测工程使用结对板热阻,”电子制冷,卷。第1号,1999年1月。